SoC Design Implementation

Advanced System Design Technologies (ASDT) specializes in logical, physical, and sign-off implementation for System-on-Chip (SoC) designs. With a team bringing over 125 years of combined experience in the ASIC industry, we offer comprehensive design services for SoCs across critical applications, including 5G, AI, automotive, mobile, image sensors, IoT, and more.

Our expert team is committed to delivering the best Performance, Power, Area, and Turnaround Time (PPAT) results for their SOC designs thereby ensuring that our clients gain a competitive edge through on-time delivery and superior design quality.

Driven by a vision centred around rapid time-to-market, our team focuses on enhancing the Quality of Results (QoR) and Turnaround Time (TAT) for complex design implementations. Our extensive expertise in design tools and methodologies makes ASDT the ideal partner for reliable tape-outs.

In addition, our strong global network of partners allows us to scale effortlessly for large SoC implementations, offering unmatched flexibility and support for every project.

* Synthesis

* RTL to Gate Equivalence Check

* Function Mode STA

* Clock Generation Module Design

* Test RTL Design

* Design For Test

* DFT Mode STA/Simulation

* DFT Vector Generation

* DFT to Gate Equivalence Check

* Place & Route

* Physical Verification

* Post-layout STA

* Layout to Gate Equivalence Check

* Design Rule Check

* GDS-Merge

* Post Layout Verification

* Design For Manufacturing

* Tape-out Supports

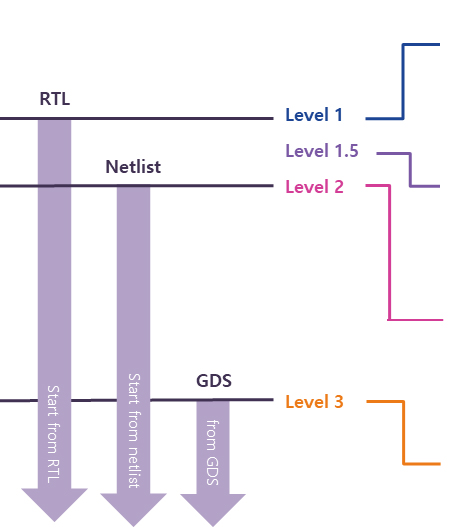

Low Power Solutions

Best Industry Low Power Solutions & Techniques with 20 Years of Tape-out Experience :

Achieving 15% Power Reduction for Cortex-A55.

Achieving 15% Power Reduction for Cortex-A55.

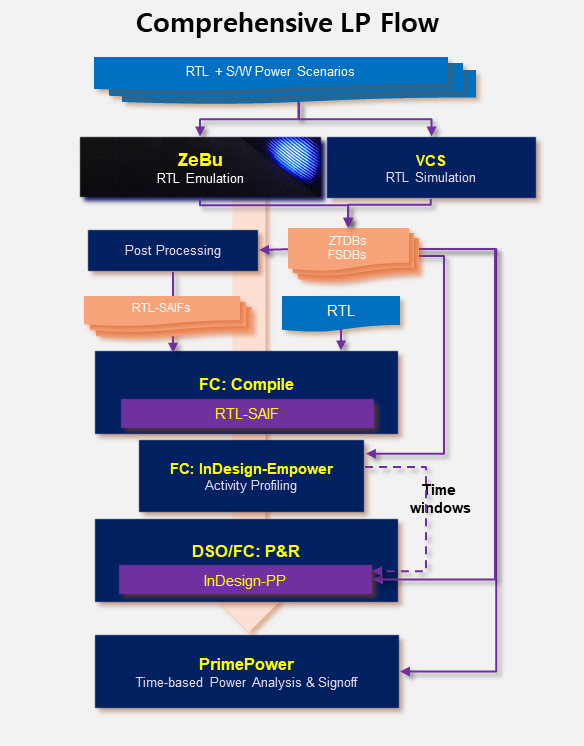

- SAIF/FSDB Flow

- FC Extreme low power recipe

- Indesign-PrimePower

- FC V-opt Flow

- DSO.ai

- Sequential power optimization

- Activity driven multibit banking

- Clock gating with SAIF

- Clock gating multi-level expansion

- Self gating and Sequential clock gating

- Restriction of low Vth lib cells

- Higher multibit banking ratio

- Enhanced low-power DesignWare

- Performance via ladder for timing critical nets

- ECGL ( Estimated Clock Gate Latency ) feature